Kenting specializes in hardware acceleration tailored for zero-knowledge computation applications. It embodies the fusion of software and hardware through SDAccel integration, specifically designed to expedite the generation of zero-knowledge proofs (ZKPs). This synergy of technology ensures efficient and faster ZKP computations, making Kenting a pivotal player in the realm of advanced cryptographic solutions.

A specialized hardware solution for zero-knowledge miners, accelerating ZK computation with fast, affordable, and accessible technology.

Hardware acceleration can enhance NTT performance by up to 50x compared to calculations done solely on a CPU.

Kenting aims to provide specialized hardware for zero-knowledge provers, enabling accelerated computation suitable for post-quantum zero-knowledge applications. For instance, in the FRI commitment protocol, which relies on mathematical problems believed to be resistant to quantum computing attacks, the proving process primarily depends on the latency of NTT operations. Kenting significantly mitigates these computational bottlenecks.

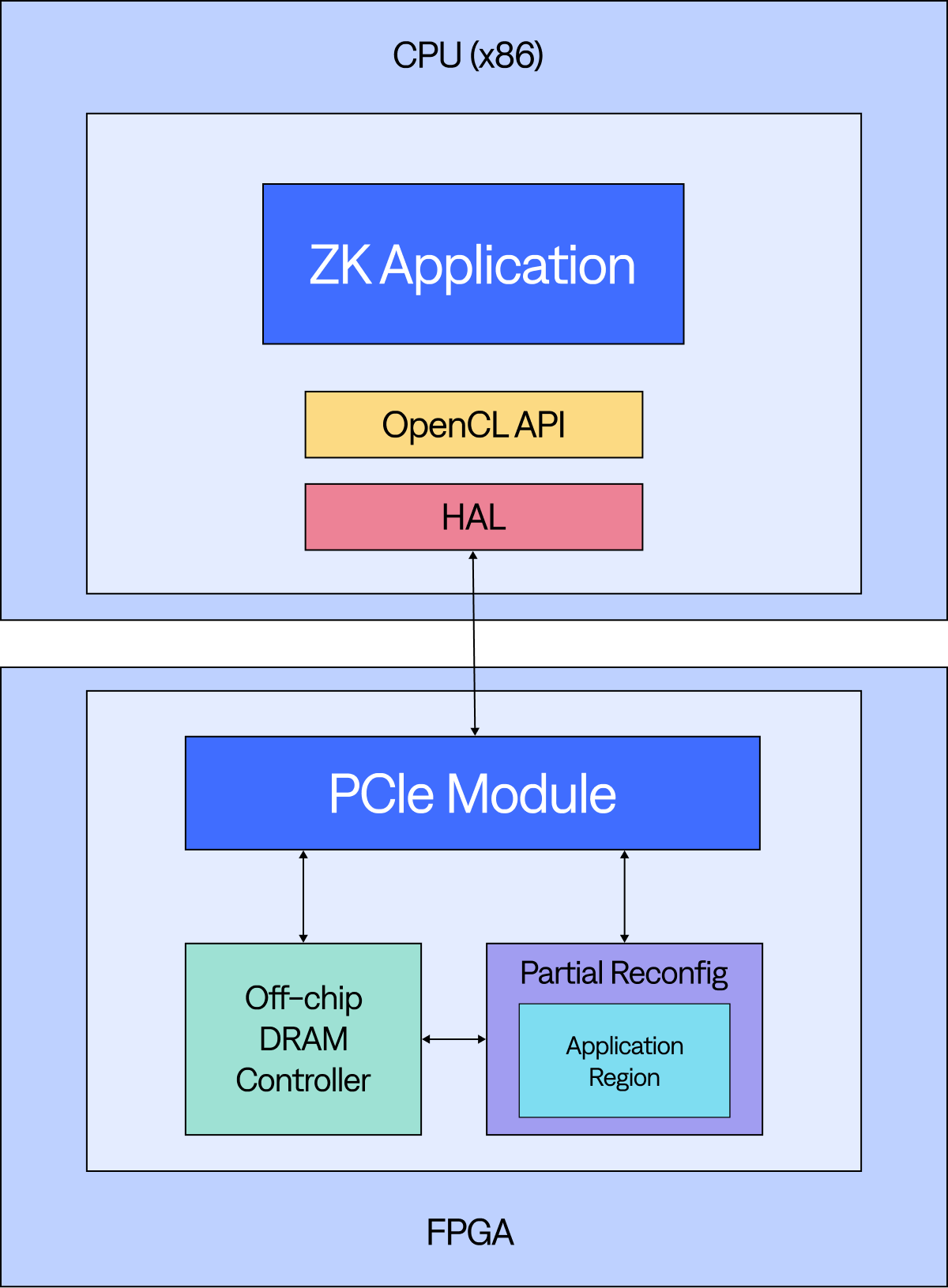

Utilizes OpenCL APIs, allowing for straightforward integration of FPGA functions into ZK applications, with highly customizable parameters for users when invoking the FPGA kernel.

Kenting is an FPGA-based application specifically crafted to accelerate zero-knowledge computations. It is developed as a dedicated hardware solution for Zero-Knowledge Proofs (ZKP). Considering the substantial computing demands of PQScale, Kenting serves as an accelerator to enhance computing speed.

Furthermore, its Acceleration Unit is tasked with calculating NTT, a crucial component in generating zero-knowledge proofs. Additionally, Kenting is strategically designed to complement 'Keelung' – a DSL programming language tailored for ZKP applications and another key product in the BTQ ZKP software suite.

In the system architecture, Kenting receives data through the PCIe Module from HAL and OpenCL API. It processes this data more rapidly than a purely software-based solution, subsequently returning the processed data to the CPU.

220 points and 224 points aim to speed up aggregating hundreds of signatures in the PQScale service.

- *NTT bit number: 128 bit

- *FPGA Resource: Xilinx U55c (LUT: 2.3M system logic cells) x1 piece

- *Speed-up compared with software executed on Linux server using single core of AMD EPYC 73F3@3.5GHz, RAM:512GB